PEDL60851C-02

# **OKI** Semiconductor ML60851C

This version: Dec. 1999

# Preliminary

# **USB Device Controller**

# **GENERAL DESCRIPTION**

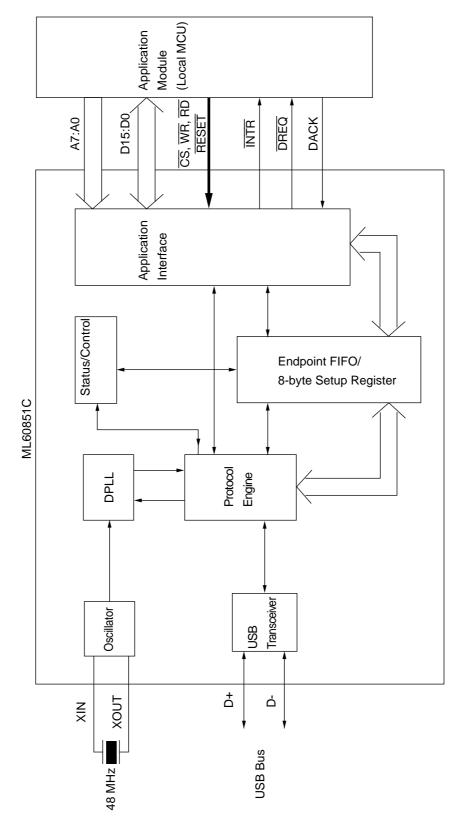

The ML60851C is a general purpose Universal Serial Bus (USB) device controller. The ML60851C provides a USB interface, control/status block, application interface, and FIFOs. The FIFO interface and two types of transfer have been optimized for BulkOut devices such as printers and BulkIn devices such as digital still cameras and image scanners. In addition, Mass Storage devices are also applicable to this device.

# **FEATURES**

- USB 1.0 compliant

- Built-in USB transceiver circuit

- Full-speed (12 Mb/sec) support

- Supports printer device class, image device class, and Mass Storage device class

- Supports three types of transfer; control transfer, bulk transfer, and interrupt transfer

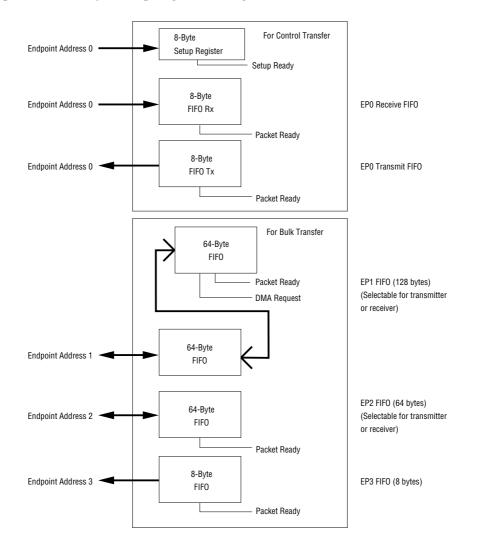

- Built-in FIFOs for control transfer

- Two 8-byte FIFOs (one for receive FIFO and the other for transmit FIFO)

- Built-in FIFOs for bulk transfer (available for either receive FIFO or transmit FIFO) One 64-byte FIFO

- Two 64-byte FIFOs

- Built-in FIFO for interrupt transfer

- One 8-byte FIFO • Supports one control endpoint, two bulk endpoint addresses, and one interrupt endpoint address

- Two 64-byte FIFOs enable fast BulkOut transfer and BulkIn transfer

- Supports 8 bit/16 bit DMA transfer

- $V_{CC}$  is 3.0 V to 3.6 V

- Supporting dual power supply enables 5 V application interface

- Built-in 48 MHz oscillator circuit

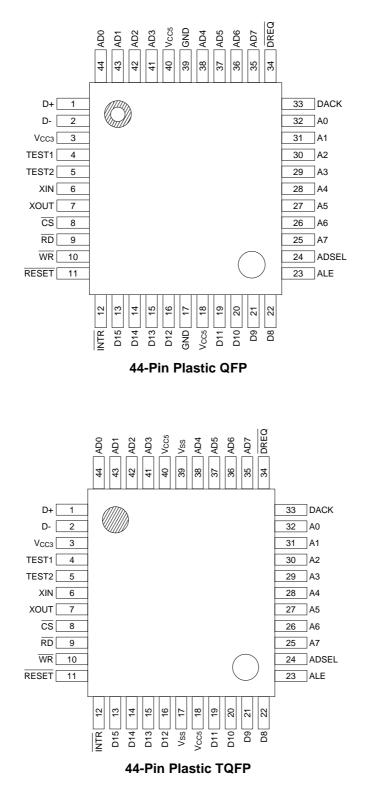

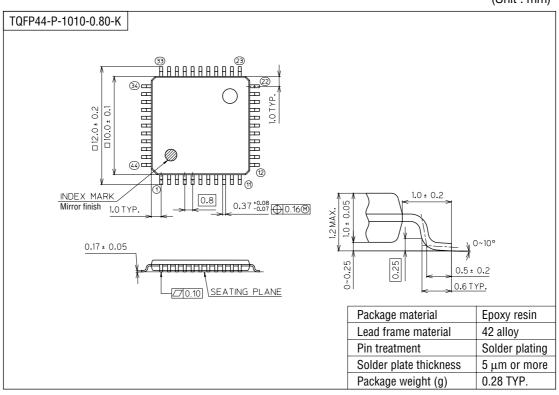

- Package options: 44-pin plastic QFP (QFP44-P-910-0.80-2K) 44-pin plastic TQFP (TQFP44-P-1010-0.80-K)

(Product name: ML60851CGA) (Product name: ML60851CTB)

ML60851C

# **BLOCK DIAGRAM**

ML60851C

# PIN CONFIGURATION (TOP VIEW)

# PIN DESCRIPTION

| Pin                   | Symbol     | Туре | Description                                                      |

|-----------------------|------------|------|------------------------------------------------------------------|

| 1,2                   | D+, D-     | I/O  | USB data                                                         |

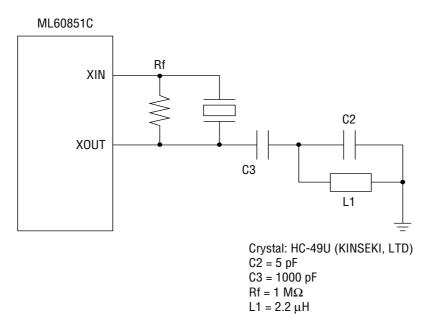

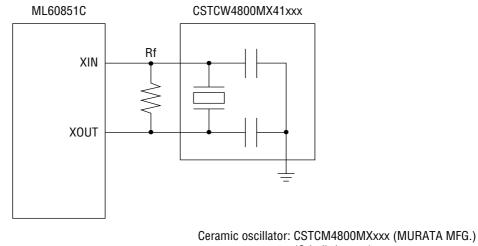

| 6, 7                  | XIN, XOUT  |      | Pins for external crystal oscillator                             |

| 4, 5                  | TEST14, 2  | -    | Test pins (normally "L")                                         |

| 13 to 16,<br>19 to 22 | D15 to D18 | I/O  | Data bus (MSB)                                                   |

| 35 to 38,<br>41 to 44 | AD7 to AD0 | I/O  | Data bus (LSB)/address inputs                                    |

| 25 to 32              | A7 to A0   |      | Address inputs                                                   |

| 8                     | CS         | Ι    | Chip select signal input pin. LOW active                         |

| 9                     | RD         | Ι    | Read signal input pin. LOW active                                |

| 10                    | WR         | Ι    | Write signal input pin. LOW active                               |

| 12                    | INTR       | 0    | Interrupt request signal output pin                              |

| 34                    | DREQ       | 0    | DMA request output pin                                           |

| 33                    | DACK       | Ι    | DMA acknowledge signal input pin                                 |

| 23                    | ALE        |      | Address latch enable signal input pin                            |

| 24                    | ADSEL      | Ι    | Address input mode select input pin. "H": address/data multiplex |

| 11                    | RESET      | Ι    | System reset signal input pin. LOW active.                       |

# INTERNAL REGISTERS

# Addresses and Names of Registers

|       | Addresse       |                 |               | Page                                   |    |

|-------|----------------|-----------------|---------------|----------------------------------------|----|

| A5:A0 | Read<br>A7, A6 | Write<br>A7, A6 | Symbol        | Register name                          |    |

| 00h   | 01b            | —               | EP0RXFIFO     | Endpoint 0 Receive FIFO Data           | 7  |

| 01h   | 01b            | —               | EP1RXFIFO     | Endpoint 1 Receive FIFO Data           | 7  |

| 02h   | 01b            | _               | EP2RXFIFO     | Endpoint 2 Receive FIFO Data           | 8  |

| 03h   | 01b            | _               |               | Reserved                               |    |

| 00h   | —              | 11b             | EP0TXFIFO     | Endpoint 0 Transmit FIFO Data          | 9  |

| 01h   | —              | 11b             | EP1TXFIFO     | Endpoint 1 Transmit FIFO Data          | 9  |

| 02h   | —              | 11b             | EP2TXFIFO     | Endpoint 2 Transmit FIFO Data          | 10 |

| 03h   | _              | 11b             | EP3TXFIFO     | Endpoint 3 Transmit FIFO Data          | 10 |

| 00h   | 11b            | 01b             | DVCADR        | Device Address Register                | 11 |

| 01h   | 11b            | 01b             | DVCSTAT       | Device Status Register                 | 11 |

| 02h   | 11b            | _               | PKTERR        | Packet Error Register                  | 13 |

| 03h   | 11b            | _               | FIFOSTAT1     | FIFO Status Register 1                 | 13 |

| 04h   | 11b            | _               | FIFOSTAT2     | FIFO Status Register 2                 | 14 |

| 08h   | 11b            | 01b             | PKTRDY        | Endpoint Packet-Ready Register         | 15 |

| 09h   | 11b            | _               | EPORXCNT      | Endpoint 0 Receive-Byte Count Register | 19 |

| 0Ah   | 11b            | _               | EP1RXCNT      | Endpoint 1 Receive-Byte Count Register | 19 |

| 0Bh   | 11b            | _               | EP2RXCNT      | Endpoint 2 Receive-Byte Count Register | 20 |

| 0Ch   | 11b            | _               |               | Reserved                               |    |

| 0Dh   | 11b            | —               | REVISION      | Revision Register                      | 21 |

| 0Eh   | —              | 01b             | CLRFIFO       | Transmit FIFO Clear Register           | 21 |

| 0Fh   | —              | 01b             | SYSCON        | System Control Register                | 22 |

| 10h   | 11b            | —               | bmRequestType | bmRequestType Setup Register           | 23 |

| 11h   | 11b            | —               | bRequest      | bRequest Setup Register                | 23 |

| 12h   | 11b            | —               | wValueLSB     | wValueLSB Setup Register               | 24 |

| 13h   | 11b            | —               | wValueMSB     | wValueMSB Setup Register               | 24 |

| 14h   | 11b            | —               | wIndexLSB     | wIndexLSB Setup Register               | 24 |

| 15h   | 11b            | —               | wIndexMSB     | wIndexMSB Setup Register               | 24 |

| 16h   | 11b            | —               | wLengthLSB    | wLengthLSB Setup Register              | 25 |

| 17h   | 11b            | —               | wLengthMSB    | wLengthMSB Setup Register              | 25 |

| 1Ah   | 11b            | 01b             | POLSEL        | Assertion Select Register              | 26 |

| 1Bh   | 11b            | 01b             | INTENBL       | Interrupt Enable Register              | 27 |

| 1Ch   | 11b            |                 | INTSTAT       | Interrupt Status Register              | 28 |

| 1Dh   | 11b            | 01b             | DMACON        | DMA Control Register                   | 30 |

| 1Eh   | 11b            | 01b             | DMAINTVL      | DMA Interval Register                  | 31 |

| 1Fh   | _              | _               |               | Reserved                               |    |

# ML60851C

|     | Addresses | 6   | Symbol   | Register name                            | Page |

|-----|-----------|-----|----------|------------------------------------------|------|

| 20h | 11b       |     | EPORXCON | Endpoint 0 Receive Control Register      | 32   |

| 21h | 11b       |     | EP0RXTGL | Endpoint 0 Receive Data Toggle Register  | 32   |

| 22h | 11b       | 01b | EP0RXPLD | Endpoint 0 Receive Payload Register      | 33   |

| 23h |           |     |          | Reserved                                 |      |

| 24h | 11b       | 01b | EP1CON   | Endpoint 1 Control Register              | 34   |

| 25h | 11b       | 01b | EP1TGL   | Endpoint 1 Data Toggle Register          | 35   |

| 26h | 11b       | 01b | EP1PLD   | Endpoint 1 Payload Register              | 35   |

| 27h | —         |     |          | Reserved                                 |      |

| 28h | _         | _   |          | Reserved                                 |      |

| 29h | —         | _   |          | Reserved                                 |      |

| 2Ah | _         | _   |          | Reserved                                 |      |

| 2Bh | _         | _   |          | Reserved                                 |      |

| 2Ch | —         | _   |          | Reserved                                 |      |

| 2Dh | —         | —   |          | Reserved                                 |      |

| 2Eh | —         | _   |          | Reserved                                 |      |

| 2Fh | —         | —   |          | Reserved                                 |      |

| 30h | 11b       | _   | EP0TXCON | Endpoint 0 Transmit Control Register     | 36   |

| 31h | 11b       | _   | EP0TXTGL | Endpoint 0 Transmit Data Toggle Register | 36   |

| 32h | 11b       | 01b | EP0TXPLD | Endpoint 0 Transmit Payload Register     | 37   |

| 33h | 11b       | 01b | EP0STAT  | Endpoint 0 Status Register               | 38   |

| 34h | 11b       | 01b | EP2CON   | Endpoint 2 Control Register              | 40   |

| 35h | 11b       | 01b | EP2TGL   | Endpoint 2 Data Toggle Register          | 41   |

| 36h | 11b       | 01b | EP2PLD   | Endpoint 2 Payload Register              | 41   |

| 37h | —         |     |          | Reserved                                 |      |

| 38h | 11b       | 01b | EP3CON   | Endpoint 3 Control Register              | 42   |

| 39h | 11b       | 01b | EP3TGL   | Endpoint 3 Data Toggle Register          | 43   |

| 3Ah | 11b       | 01b | EP3PLD   | Endpoint 3 Payload Register              | 43   |

| 3Bh | _         |     |          | Reserved                                 |      |

| 3Ch | —         | —   |          | Reserved                                 |      |

| 3Dh | _         | _   |          | Reserved                                 |      |

| 3Eh | —         | —   |          | Reserved                                 |      |

| 3Fh | _         |     |          | Reserved                                 |      |

# Addresses and Names of Registers (Continued)

#### **FUNCTIONS OF REGISTERS**

## End Point 0 Receive FIFO (EP0RXFIFO)

| Read address  | 40h |

|---------------|-----|

| Write address | -   |

|                        | D7                   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|----------------------|----|----|----|----|----|----|----|

| After a hardware reset | х                    | х  | х  | х  | х  | х  | х  | х  |

| After a bus reset      | х                    | х  | х  | х  | х  | х  | х  | х  |

| Definition             | EP0 Receive data (R) |    |    |    |    |    |    |    |

The receive data from the host computer in the data state during a control Write transfer is stored in EP0RXFIFO. The EP0 receive data can be read out by the local MPU through reading the address 40h when the ML60851C issues an EP0 receive packet ready interrupt request. It is possible to read successively the data in the packet by reading continuously.

The EP2RXFIFO is cleared under the following conditions:

- 1. When the local MPU resets the EP0 receive packet ready bit (A "1" is written in PKTRDY(0)).

- 2. When a setup packet is received.

- 3. When the local MCU writes a "0" in the stall bit (EP0STAT(2)).

## End Point 1 Receive FIFO (EP1RXFIFO)

| Read address  | 41h |

|---------------|-----|

| Write address | _   |

|                        | D7                   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|----------------------|----|----|----|----|----|----|----|

| After a hardware reset | х                    | х  | х  | х  | х  | х  | х  | х  |

| After a bus reset      | х                    | х  | х  | х  | х  | х  | х  | х  |

| Definition             | EP1 Receive data (R) |    |    |    |    |    |    |    |

It is possible to read out the EP1 receive data by reading the address 41h. When EP1 is set for bulk reception (BULK OUT), The local MCU should read EP1RXFIFO when the ML60851C issues an EP2 packet ready interrupt request. It is possible to read successively the data in the packet by reading continuously. When the data transfer direction of EP1 is set as "Transmit", all accesses to this address will be invalid.

The EP1RXFIFO is cleared under the following conditions:

- 1. When an OUT token is received for EP1.

- 2. When the EP1 receive packet ready bit is reset. (A "1" is written in PKTRDY(1).)

- 3. When the local MCU writes a "0" in the stall bit (EP1CON(1)).

Even when a DMA read with a 16-bit width is made from EP1RXFIFO, the address is A7:A0 = 41h.

## ML60851C

# End Point 2 Receive FIFO (EP2RXFIFO)

| Read address           |                      | 42h         |  |  |   |    |    |    |

|------------------------|----------------------|-------------|--|--|---|----|----|----|

| Write address          | _                    |             |  |  |   |    |    |    |

|                        |                      |             |  |  |   |    |    |    |

|                        | D7                   | D7 D6 D5 D4 |  |  |   | D2 | D1 | D0 |

| After a hardware reset | х                    | x x x x     |  |  | х | х  | х  | х  |

| After a bus reset      | x x x x              |             |  |  | х | х  | х  | х  |

| Definition             | EP2 Receive data (R) |             |  |  |   |    |    |    |

It is possible to read out the EP2 receive data by reading the address 42h. When EP2 is set for bulk reception (Bulk OUT), the local MCU should read EP2RXFIFO when the ML60851C issues an EP2 packet ready interrupt request. It is possible to read successively the data in the packet by reading continuously. When the data transfer direction of EP2 is set as 'Transmit', all accesses to this address will be invalid.

The EP2RXFIFO is cleared under the following conditions:

1. When an OUT token is received for EP2.

2. When the EP2 receive packet ready bit is reset. (A "1" is written in PKTRDY(2).)

3. When the local MCU writes a "0" in the stall bit (EP2CON(1)).

## ML60851C

## End Point 0 Transmit FIFO (EP0TXFIFO)

| Read address           | -           | _       |     |        |          |     |    |    |

|------------------------|-------------|---------|-----|--------|----------|-----|----|----|

| Write address          | C0h         |         |     |        |          |     |    |    |

|                        |             |         |     |        |          |     |    |    |

|                        | D7 D6 D5 D4 |         |     | D4     | D3       | D2  | D1 | D0 |

| After a hardware reset | х           | х       | х   | х      | х        | х   | х  | х  |

| After a bus reset      | х           | x x x x |     |        |          | х   | х  | х  |

| Definition             |             |         | EP0 | Transr | nit data | (W) |    |    |

The EP0 transmit data can be written in by writing to the address C0h. The receive data from the host in the data stage during a control read transfer is stored in EP0TXFIFO. When the ML60851C issues an EP0 transmit packet ready interrupt request, the local MCU writes the transmit data to the address C0h. It is possible to write the packet data successively by writing continuously.

The EP0 TXFIFO is cleared under the following conditions:

- 1. When an ACK is received from the host for the data transmission from EP0.

- 2. When a setup packet is received.

### End Point 1 Transmit FIFO (EP1TXFIFO)

| Read address  | —   |

|---------------|-----|

| Write address | C1h |

|                        | D7                    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|-----------------------|----|----|----|----|----|----|----|

| After a hardware reset | х                     | х  | х  | х  | х  | х  | х  | х  |

| After a bus reset      | х                     | х  | х  | х  | х  | х  | х  | х  |

| Definition             | EP1 Transmit data (W) |    |    |    |    |    |    |    |

The EP1 transmit data can be written in by writing to the address C1h. When EP1 has been set for bulk transmission (BULK IN), The local MCU should write the transmit data in EP1TXFIFO when the ML60851C issues an EP1 packet ready interrupt request. It is possible to write the packet data successively by writing continuously. When the data transfer direction of EP1 is set as 'Receive', all accesses to this address will be invalid.

The EP1 transmit FIFO is cleared under the following conditions:

1. When an ACK is received from the host for the data transmission from EP1.

2. When the local MCU writes a "1" in the EP1FIFO clear bit (CLRFIFO(1)).

Even when a DMA write with a 16-bit width is made in EP1TXFIFO, the address is A7:A0 = 41h.

### ML60851C

## End Point 2 Transmit FIFO (EP2TXFIFO)

| Read address           | d address –           |             |   |   |    |    |    |    |

|------------------------|-----------------------|-------------|---|---|----|----|----|----|

| Write address          | C2h                   |             |   |   |    |    |    |    |

|                        |                       |             |   |   |    |    |    |    |

|                        | D7                    | D7 D6 D5 D4 |   |   | D3 | D2 | D1 | D0 |

| After a hardware reset | х                     | х           | х | х | х  | х  | х  | х  |

| After a bus reset      | х                     | х           | х | х | х  | х  | х  | х  |

| Definition             | EP2 Transmit data (W) |             |   |   |    |    |    |    |

The EP2 transmit data can be written in by writing to the address C2h. When EP2 has been set for bulk transmission (BULK IN), The local MCU should write the transmit data in EP1TXFIFO when the ML60851C issues an EP2 packet ready interrupt request. It is possible to write the packet data successively by writing continuously. When the data transfer direction of EP2 is set as "Receive", all accesses to this address will be invalid.

The EP2 TXFIFO is cleared under the following conditions:

- 1. When an ACK is received from the host for the data transmission from EP2.

- 2. When the local MCU writes a "1" in the EP2FIFO clear bit (CLRFIFO(2)).

# End Point 3 Transmit FIFO (EP3TXFIFO)

| Read address  | _   |

|---------------|-----|

| Write address | C3h |

|               |     |

|                        | D7                    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|-----------------------|----|----|----|----|----|----|----|

| After a hardware reset | х                     | х  | х  | х  | х  | х  | х  | х  |

| After a bus reset      | х                     | х  | х  | х  | х  | х  | х  | х  |

| Definition             | EP3 Transmit data (W) |    |    |    |    |    |    |    |

The EP3 transmit data can be written in by writing to the address C3h. Make the local MCU write the transmit data in EP3TXFIFO when the ML60851C issues an EP3 packet ready interrupt request. It is possible to write the packet data successively by writing continuously.

The EP3 TXFIFO is cleared under the following conditions:

- 1. When an ACK is received from the host for the data transmission from EP3.

- 2. When the local MCU writes a "1" in the EP3FIFO clear bit (CLRFIFO(3)).

#### ML60851C

## **Device Address Register (DVCADR)**

| Read address           |                      | С  | 0h |    |    |    |    |    |

|------------------------|----------------------|----|----|----|----|----|----|----|

| Write address          | 40h                  |    |    |    |    |    |    |    |

|                        |                      |    |    |    |    |    |    |    |

|                        | D7                   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| After a hardware reset | 0                    | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0                    | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | Device address (R/W) |    |    |    |    |    |    |    |

The local MCU writes in this register the device address given by the SET\_ADDRESS command from the host. Thereafter, the ML60851C responds only to the token specifying this address among all the tokens from the host computer. The default value is the address D6:D0 = 00h.

Note 1: It is possible to carry out addressing using a 7-bit address because up to 127 devices can be connected according to the USB standard.

Note 2: The bit D7 is fixed at "0", and even if a "1" is written in the bit D7, it will be invalid.

# **Device State Register (DVCSTAT)**

| Read address           |    | С  | 1h |    |    |    |    |    |                                                                                                                                                                                                          |

|------------------------|----|----|----|----|----|----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write address          |    | 4  | 1h |    |    |    |    |    |                                                                                                                                                                                                          |

|                        |    | 1  | 1  |    | 1  | 1  | 1  |    |                                                                                                                                                                                                          |

|                        | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                                                                          |

| After a hardware reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |                                                                                                                                                                                                          |

| After a bus reset      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |                                                                                                                                                                                                          |

| Definition             | 0  | 0  |    |    |    |    |    |    |                                                                                                                                                                                                          |

|                        |    |    |    |    |    |    |    |    | <ul> <li>Default state (R/W)</li> <li>Address state (R/W)</li> <li>Configuration state (R/W)</li> <li>Suspend state (R)</li> <li>Remote wake-up (R/W)</li> <li>USB bus reset status clear (W)</li> </ul> |

This is a register for displaying the status of the device. The functions of the different bits are described below: The bits D7 and D6 are fixed at "0" and even if a "1" is written in these bits, the write operation will be invalid.

#### Default state:

This bit is asserted in the initial state. The default state is valid from the time the power is switched ON and the hardware resetting is complete. There is no need to write a "0" in this bit.

#### Address state:

When a SET\_ADDRESS request arrives, the local MCU writes the device address in the device address register. If necessary, by writing a "1" in this bit also at that time, it is possible to give an indication that the ML60851C has entered the address state. Since the content of this bit does not affect the operation of the ML60851C, there is no need to write in this bit if it will not be read out.

#### Configuration state:

When the local MPU asserts the configuration bits EP1CON, EP2CON, or EP3CON in response to a SET\_CONFIGURATION request from the host computer when this IC is in the address state, by writing a "1" in this bit also, if necessary, at that time, it is possible to give an indication that the ML60851C has entered the configuration state. Since the content of this bit does not affect the operation of the ML60851C, there is no need to write in this bit if it will not be read out.

#### Remarks:

When all these three states are "1", it means that this IC is normally operating. However, since these bits do not affect the operation of the ML60851C, there is no need to write in these bits if they will not be read out.

Suspend state:

When the idle condition continues for more than 3ms in the USB bus, the ML60851C automatically asserts this bit thereby indicating that it is going into the suspend state. At the same time, bit D6 of the interrupt status register INTSTAT is asserted and the  $\overline{INTR}$  pin is asserted. With this, the local MCU can suppress the current consumption.

This bit is deasserted when the EOP of any type of packet is received.

#### Remote wake-up:

The ML60851C is in the suspend state, the remote wake-up function is activated when the local MCU asserts this bit. When this bit is written while 5ms have not yet elapsed in the idle condition, the remote wake-up signal is output after waiting for the idle condition to continue for the full 5ms period. Further, when this bit is written after the idle condition has persisted for 5ms or more, the remote wake-up signal is output immediately after this bit is written. This bit is deasserted automatically when the suspend state is released by receiving the resume instruction over the USB bus.

## USB bus reset status clear:

When the ML60851C is in the USB bus reset interrupt state (bit D5 of the interrupt status register, that is the USB bus reset interrupt status bit is "1" and the  $\overline{INTR}$  pin is asserted), it is possible to clear the interrupt status by writing a "1" in this bit. (This makes the USB bus reset interrupt status bit "0" and deassertes  $\overline{INTR}$ .) Although this bit can be read out, the read out value will always be "0".

## ML60851C

## Packet Error Register (PKTERR)

| Read address           |    | С  | 2h |    |    |    |            |            |                                                                                                                           |

|------------------------|----|----|----|----|----|----|------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| Write address          |    | -  |    |    |    |    |            |            |                                                                                                                           |

|                        | D7 | DC | Dr |    | Do | Do | <b>D</b> 4 | <b>D</b> 0 |                                                                                                                           |

|                        | D7 | D6 | D5 | D4 | D3 | D2 | D1         | D0         |                                                                                                                           |

| After a hardware reset | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0          |                                                                                                                           |

| After a bus reset      | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0          |                                                                                                                           |

| Definition             | 0  | 0  | 0  | 0  |    |    |            |            |                                                                                                                           |

|                        |    |    |    |    |    |    |            |            | <ul> <li>Bit stuff error (R)</li> <li>Data CRC error (R)</li> <li>Address CRC error (R)</li> <li>PID Error (R)</li> </ul> |

Each bit is asserted when the corresponding error occurs and is deasserted when SOP is received. This register is used to report the error information. This register is useful for the tests during development, or for preparing the error frequency measurement report. This register is not particularly required for the specification of commercial a product.

# FIFO Status Register 1 (FIFOSTAT1)

| Read address           |    | С  | 3h |    |    |    |    |    |                           |

|------------------------|----|----|----|----|----|----|----|----|---------------------------|

| Write address          |    | -  |    |    |    |    |    |    |                           |

|                        | I  |    | I  |    | I  |    |    |    | -                         |

|                        | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | _                         |

| After a hardware reset | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  |                           |

| After a bus reset      | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  |                           |

| Definition             | 0  | 0  | 0  | 0  |    |    |    |    |                           |

|                        |    |    |    |    |    |    |    |    |                           |

|                        |    |    |    |    |    |    |    |    | - Receive FIFO0 Full (R)  |

|                        |    |    |    |    |    |    |    |    | - Receive FIFO0 Empty (R) |

|                        |    |    |    |    |    |    |    |    | — FIFO1 Full (R)          |

|                        |    |    |    |    |    |    |    |    | — FIFO1 Empty (R)         |

This register reports the statuses of the EPORXFIFO and the FIFO for EP1. Normally, there is no need to read this register because it is sufficient to read the packet ready status before reading out or writing in a FIFO.

| Receive FIFO0 Full:  | This bit becomes "1" when 8-bytes of data are stored in the EPORXFIFO. This bit is not set to "1" when a packet less than 8 bytes long (a short packet) is stored in. |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive FIFO0 Empty: | This bit will be "1" when the EPORXFIFOO is empty.                                                                                                                    |

| FIFO1 Full:          | This bit becomes "1" when 64 bytes of data is stored in the FIFO for EP1. This is true                                                                                |

|                      | during both transmission and reception. This bit does not become "1" in the case of a                                                                                 |

|                      | short packet. The FIFO for EP1 has a two-layer structure and can store up to 128                                                                                      |

|                      | bytes of data. This bit indicates the status of the FIFO in which data being written at                                                                               |

|                      | that time. In other words, this bit indicates the status of the FIFO into which the host                                                                              |

|                      | computer is writing data when EP1 is receiving data, and of the FIFO into which the                                                                                   |

|                      | local MCU is writing data when EP1 is transmitting data.                                                                                                              |

| FIFO1 Empty:         | This bit becomes "1" when the FIFO for EP1 is empty. This is true during both                                                                                         |

|                      | transmission and reception. The FIFO for EP1 has a two-layer structure and can store                                                                                  |

|                      | up to 128 bytes of data. This bit indicates the status of the FIFO which is being read                                                                                |

|                      | out at that time.                                                                                                                                                     |

# ML60851C

# FIFO0 Status Register 2 (FIFOSTAT2)

| Read address           |    | С  | 4h |    |    |    |    |    |                                                                                                                                                                                 |

|------------------------|----|----|----|----|----|----|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write address          |    | -  | _  |    |    |    |    |    |                                                                                                                                                                                 |

|                        |    | 1  | 1  |    | 1  | 1  | 1  |    |                                                                                                                                                                                 |

|                        | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                                                 |

| After a hardware reset | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |                                                                                                                                                                                 |

| After a bus reset      | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |                                                                                                                                                                                 |

| Definition             | 0  | 0  |    |    |    |    |    |    |                                                                                                                                                                                 |

|                        |    |    |    |    |    |    |    |    | <ul> <li>Transmit FIFO0 Full (R)</li> <li>Transmit FIFO0 Empty (R)</li> <li>FIFO2 Full (R)</li> <li>FIFO2 Empty (R)</li> <li>FIFO3 Full (R)</li> <li>FIFO3 Empty (R)</li> </ul> |

This register reports the statuses of the EP0TXFIFO, the FIFO for EP2, and the FIFO for EP3. Normally, there is no need to read this register because it is sufficient to read the packet ready status before reading out or writing in a FIFO.

| Transmit FIFO0 Full: | This bit becomes "1" when 8-bytes of data is stored in the EP0TXFIFO. This bit is      |

|----------------------|----------------------------------------------------------------------------------------|

|                      | not set to "1" when a packet less than 8 bytes (a short packet) is written in.         |

| Transmit FIFO0 Empty | : This bit will be "1" when the EP0 transmit FIFO0 is empty.                           |

| FIFO2 Full:          | This bit becomes "1" when 64 bytes of data is either stored or written in the FIFO for |

|                      | EP2. This bit does not become "1" in the case of a short packet.                       |

| FIFO2 Empty:         | This bit becomes "1" when the FIFO of EP2 is empty.                                    |

| FIFO3 Full:          | This bit becomes "1" when 64 bytes are written in the FIFO for EP3. This bit does not  |

|                      | become "1" in the case of a short packet.                                              |

| FIFO3 Empty:         | This bit becomes "1" when the FIFO for EP3 is empty.                                   |

## End Point Packet Ready Register (PKTRDY)

This register indicates whether or not the preparations for reading out or writing in a packet data have been completed. In addition, this register is also used for controlling the handshake packet (ACK/NAK)

| Read address           |    | С  | 8h |    |            |            |    |    |                                                                                                                                                                                                                                      |

|------------------------|----|----|----|----|------------|------------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write address          |    | 4  | 8h |    |            |            |    |    |                                                                                                                                                                                                                                      |

|                        | DZ | DC | Dr | D4 | <b>D</b> 2 | <b>D</b> 2 | DI | DO |                                                                                                                                                                                                                                      |

|                        | D7 | D6 | D5 | D4 | D3         | D2         | D1 | D0 |                                                                                                                                                                                                                                      |

| After a hardware reset | 0  | 0  | 0  | 0  | 0          | 0          | 0  | 0  |                                                                                                                                                                                                                                      |

| After a bus reset      | 0  | 0  | 0  | 0  | 0          | 0          | 0  | 0  |                                                                                                                                                                                                                                      |

| Definition             |    |    |    |    | 0          |            |    |    |                                                                                                                                                                                                                                      |

|                        |    |    |    |    |            |            |    |    | <ul> <li>EP0 Receive packet ready (R/Reset)</li> <li>EP1 Receive packet ready (R/Reset)</li> <li>EP2 Receive packet ready (R/Reset)</li> <li>EP0 Transmit packet ready (R/Set)</li> <li>EP1 Transmit packet ready (R/Set)</li> </ul> |

|                        |    |    |    |    |            |            |    |    | EP2 Transmit packet ready (R/Set)<br>EP3 Transmit packet ready (R/Set)                                                                                                                                                               |

This is the register for indicating that the local MCU can request a read/write of the FIFO for each EP. The logical sums (AND) of each of these bits and the corresponding bits of INTENBL become the bits of INTSTAT.

The ML60851C asserts a receive packet ready bit (set to "0") and generates an interrupt cause. The local MCU resets the receive packet ready bit after completion of the interrupt servicing (such as taking out data from the corresponding receive FIFO, etc.,).

The ML60851C deasserts a transmit packet ready bit and generates an interrupt cause. The local MCU sets the receive packet ready bit after completion of the interrupt servicing (such as writing data in the corresponding transmit FIFO, etc.,).

The bit D3 is fixed at "0", and even if a "1" is written in this bit, that write operation will be invalid. The operations of the different bits of PKTRDY are described in detail below.

# EP0 Receive packet ready bit (D0)

This bit can be read by the local MCU. Further, this bit can be set to "0" by writing "1" to the D0 bit.

The conditions of asserting and deasserting this bit are the following.

| Bit name                      | Asserting condition                                                                                                               | Action when asserted                                                                                                      |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| EP0 Receive packet ready (D0) | <ol> <li>When data is received in EP0<br/>and storing of one packet of<br/>receive data in EP0RXFIFO is<br/>completed.</li> </ol> | EP0 is locked (that is, an NAK is<br>returned automatically when a data<br>packet is received from the host<br>computer). |

|                               | 2. When a setup packet is received during a control Read or a control Write transfer.                                             | (In the case of the asserting condition 1, the local MCU can read EP0RXFIFO.)                                             |

| Bit name                      | Deasserting condition                                                                                                                                                         | Action when deasserted        |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| EP0 Receive packet ready (D0) | <ol> <li>When the local MCU resets<br/>(writes a "1" in) this bit.</li> <li>When the local MCU resets the<br/>setup ready bit during a control<br/>Write transfer.</li> </ol> | Reception is possible in EP0. |

R/Reset:Reading possible/ Reset when a "1" is writtenR/Set:Reading possible/ Set when a "1" is written

# EP1 Receive Packet Ready Bit (D1)

This bit can be read by the local MCU. Further, this bit can be set to "0" by writing "1" to the D1 bit. The conditions of asserting and deasserting this bit are the following. EP1 has a two-layer FIFO, and even the packet ready bits are present independently for layer A and layer B. The switching between these two layers is done automatically by the ML60851C.

| Bit name                      | Asserting condition                                                               | Action when asserted                                                                                                    |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EP1 Receive packet ready (D1) | When an error-free packet is received in either layer A or layer B.               | The local MCU can read the<br>EP1RXFIFO. EP1 is locked when<br>both layer A and layer B have<br>received a packet data. |  |  |  |

|                               |                                                                                   |                                                                                                                         |  |  |  |

| Bit name                      | Deasserting condition                                                             | Action when deasserted                                                                                                  |  |  |  |

| EP1 Receive packet ready (D1) | When the local MCU resets (writes a "1") in the bits of both layer A and layer B. | Reception is possible in EP1 when at least one of the bits of layer A and layer B has been reset.                       |  |  |  |

See the explanation of the operation of the two-layer FIFO given in the Section on 'Functional Description'.

# EP2 Receive Packet Ready Bit (D2)

This bit can be read by the local MCU. Further, this bit can be set to "0" by writing "1" to the D2 bit. The conditions of asserting and deasserting this bit are the following.

| Bit name                      | Asserting condition                                   | Action when asserted               |  |  |

|-------------------------------|-------------------------------------------------------|------------------------------------|--|--|

| EP2 Receive packet ready (D2) | When an error-free packet is received.                | EP2 is locked.                     |  |  |

|                               | -                                                     |                                    |  |  |

| Bit name                      | Deasserting condition                                 | Action when deasserted             |  |  |

| EP2 Receive packet ready (D2) | When the local MCU resets (writes a "1" in) this bit. | Data reception is possible in EP2. |  |  |

## EP0 Transmit Packet Ready Bit (D4)

This bit can be read by the local MCU. Further, this bit can be set to "1" by writing "1" to the D4 bit. The conditions of asserting and deasserting this bit are the following.

| Bit name                       | Asserting condition                                                                                    | Action when asserted                                                                                       |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| EP0 Transmit packet ready (D4) | When the local MCU sets this bit.                                                                      | Data transmission is possible from EP0.                                                                    |  |  |

|                                |                                                                                                        |                                                                                                            |  |  |

| Bit name                       | Deasserting condition                                                                                  | Action when deasserted                                                                                     |  |  |

| EP0 Transmit packet ready (D4) | 1. When an ACK is received from the<br>host computer in response to the<br>data transmission from EP0. | EP0 is locked. In other words, an NAK is returned automatically when an IN token is received from the host |  |  |

|                                | 2. When a setup packet is received.                                                                    | computer.                                                                                                  |  |  |

# EP1 Transmit Packet Ready Bit (D5)

This bit can be read by the local MCU. Further, this bit can be set to "1" by writing "1" to the D5 bit. The conditions of asserting and deasserting this bit are the following. EP1 has a two-layer FIFO, and even the packet ready bits are present independently for layer A and layer B. The switching between these two layers is performed automatically by the ML60851C.

| Bit name                       | Asserting condition                                                                                      | Action when asserted                                                                                                    |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EP1 Transmit packet ready (D5) | When the local MCU has set the bits of both layer A and layer B.                                         | Data transmission is possible from<br>EP1 when the bit for at least one of<br>layer A and layer B has been<br>asserted. |  |  |  |

|                                |                                                                                                          |                                                                                                                         |  |  |  |

| Bit name                       | Deasserting condition                                                                                    | Action when deasserted                                                                                                  |  |  |  |

| EP1 Transmit packet ready (D5) | When an ACK is received from the host computer for the data transmission from either layer A or layer B. | EP1 is locked when both layer A and<br>layer B have not prepared the<br>transmit data.                                  |  |  |  |

See the explanation of the operation of the two-layer FIFO given in the Section on 'Functional Description'.

# EP2 Transmit Packet Ready Bit (D6)

This bit can be read by the local MCU. Further, this bit can be set to "1" by writing "1" to the D6 bit. The conditions of asserting and negating this bit are the following.

| Bit name                       | Asserting condition                                                                           | Action when asserted                    |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| EP2 Transmit packet ready (D6) | When the local MCU has set this bit.                                                          | Data transmission is possible from EP2. |  |  |  |

|                                |                                                                                               |                                         |  |  |  |

| Bit name                       | Deasserting condition                                                                         | Action when deasserted                  |  |  |  |

| EP2 Transmit packet ready (D6) | When an ACK is received from the host computer in response to the data transmission from EP2. | EP2 is locked.                          |  |  |  |

## EP3 Transmit Packet Ready Bit (D7)

This bit can be read by the local MCU. Further, this bit can be set to "1" by writing "1" to the D7 bit. The conditions of asserting and deasserting this bit are the following.

| Bit name                       | Asserting condition                                                                           | Action when asserted                    |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| EP3 Transmit packet ready (D7) | When the local MCU has set this bit.                                                          | Data transmission is possible from EP3. |  |  |

|                                |                                                                                               |                                         |  |  |

| Bit name                       | Deasserting condition                                                                         | Action when deasserted                  |  |  |

| EP2 Transmit packet ready (D7) | When an ACK is received from the host computer in response to the data transmission from EP3. | EP3 is locked.                          |  |  |

## End Point 0 Receive Byte Count Register (EP0RXCNT)

| Read address           |    | C9h                   |    |    |    |    |    |    |

|------------------------|----|-----------------------|----|----|----|----|----|----|

| Write address          |    | —                     |    |    |    |    |    |    |

|                        |    |                       |    |    |    |    |    | ·  |

|                        | D7 | D6                    | D5 | D4 | D3 | D2 | D1 | D0 |

| After a hardware reset | 0  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | 0  | Byte count of EP0 (R) |    |    |    |    |    |    |

The ML60851C automatically counts the number of bytes in the packet being received by EP0 and stored it in this register. Although the counting is performed up to the maximum packet size entered in the payload register in the case of a full packet, the count will be less than this value in the case of a short packet. The local MCU refers to this value and reads the data of one packet from the EP0RXFIFO.

The EP0 receive byte count register is cleared under the following conditions:

- 1. When the local MCU resets the EP0 receive packet ready bit (by writing a "1" in PKTRDY(0)).

- 2. When a setup packet is received.

- 3. When the local MCU writes a "0" in the stall bit (EP0STAT(2)).

# End Point 1 Receive Byte Count Register (EP1RXCNT)

| Read address  | CAh |

|---------------|-----|

| Write address | —   |

|                        | D7 | D6                    | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|----|-----------------------|----|----|----|----|----|----|

| After a hardware reset | 0  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0  | 0 0 0 0 0 0 0         |    |    |    | 0  |    |    |

| Definition             | 0  | Byte count of EP1 (R) |    |    |    |    |    |    |

The ML60851C automatically counts the number of bytes in the packet being received by EP1 and stored it in this register. Although the counting is performed up to the maximum packet size entered in the payload register in the case of a full packet, the count will be less than this value in the case of a short packet. The local MCU refers to this value and reads the data of one packet from the EP1 receive FIFO.

This register is invalid when the EP1 transfer direction is set as 'Transmit'.

The EP1 receive byte count register is cleared under the following conditions:

- 1. When an OUT token is received for EP1.

- 2. When the EP1 receive packet ready bit is reset (by writing a "1" in PKTRDY(1)).

- 3. When the local MCU writes a "0" in the stall bit (EP1CON(1)).

## End Point 2 Receive Byte Count Register (EP2RXCNT)

| Read address           |    | С                     | Bh |    |    |    |    |    |

|------------------------|----|-----------------------|----|----|----|----|----|----|

| Write address          |    |                       |    |    |    |    |    |    |

|                        |    |                       |    |    |    |    |    |    |

|                        | D7 | D6                    | D5 | D4 | D3 | D2 | D1 | D0 |

| After a hardware reset | 0  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | 0  | Byte Count of EP2 (R) |    |    |    |    |    |    |

The ML60851C automatically counts the number of bytes in the packet being received by EP2 and stored it in this register. Although the counting is performed up to the maximum packet size entered in the payload register in the case of a full packet, the count will be less than this value in the case of a short packet. The local MCU refers to this value and reads the data of one packet from the EP2RXFIFO.

This register is invalid when the EP2 transfer direction is set as 'Transmit'.

The EP2 receive byte count register is cleared under the following conditions:

- 1. When an OUT token is received for EP2.

- 2. When the EP2 receive packet ready bit is reset (by writing a "1" in PKTRDY(2)).

- 3. When the local MCU writes a "0" in the stall bit (EP2CON(1)).

# **Revision Register (REVISION)**

| Read address           |                      | CDh |    |    |    |    |    |    |

|------------------------|----------------------|-----|----|----|----|----|----|----|

| Write address          |                      | -   | _  |    |    |    |    |    |

|                        |                      |     |    |    |    |    |    |    |

|                        | D7                   | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

| After a hardware reset |                      |     |    |    |    |    |    |    |

| After a bus reset      | Revision No. of Chip |     |    |    |    |    |    |    |

| Definition             |                      |     |    |    |    |    |    |    |

# Transmit FIFO Clear Register (CLRFIFO)

| Read address           |    | _  | _        |         |         |          |    |    |                                                                                                               |

|------------------------|----|----|----------|---------|---------|----------|----|----|---------------------------------------------------------------------------------------------------------------|

| Write address          |    | 4  | Eh       |         |         |          |    |    |                                                                                                               |

|                        |    |    |          |         |         |          |    |    |                                                                                                               |

|                        | D7 | D6 | D5       | D4      | D3      | D2       | D1 | D0 |                                                                                                               |

| After a hardware reset |    | C  | Cannot I | be read |         |          |    |    |                                                                                                               |

| After a bus reset      |    | C  | Cannot l | be read | (indete | erminate | e) |    |                                                                                                               |

| Definition             | 0  | 0  | 0        |         |         |          |    | 0  |                                                                                                               |

|                        |    |    |          |         |         |          |    |    | <ul> <li>EP1 Transmit FIFO Clear</li> <li>EP2 Transmit FIFO Clear</li> <li>EP3 Transmit FIFO Clear</li> </ul> |

EP1 to EP3 FIFO Clear: When each EP has been set for transmission, by writing a "1" in these bits, the corresponding FIFOs are cleared at the Write pulse and also the corresponding EP Packet Ready bits are reset.

# System Control Register (SYSCON)

| Read address            |                                                   | -                                                                             | _                                                                       |                                                         |                                              |                                                              |                                                                 |                                                     |                                                                                                                                                                    |  |

|-------------------------|---------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Write address           |                                                   | 4                                                                             | Fh                                                                      |                                                         |                                              |                                                              |                                                                 |                                                     |                                                                                                                                                                    |  |

|                         |                                                   |                                                                               |                                                                         |                                                         | <b>D</b> 0                                   | <b>D</b> 0                                                   | 54                                                              |                                                     |                                                                                                                                                                    |  |

|                         | D7                                                | D6                                                                            | D5                                                                      | D4                                                      | D3                                           | D2                                                           | D1                                                              | D0                                                  |                                                                                                                                                                    |  |

| After a hardware reset  |                                                   | Cannot be read (indeterminate)                                                |                                                                         |                                                         |                                              |                                                              |                                                                 |                                                     |                                                                                                                                                                    |  |

| After a bus reset       | Cannot be read (indeterminate)                    |                                                                               |                                                                         |                                                         |                                              |                                                              |                                                                 |                                                     |                                                                                                                                                                    |  |

| Definition              |                                                   |                                                                               |                                                                         |                                                         | 0                                            | 0                                                            | 0                                                               |                                                     |                                                                                                                                                                    |  |

| Software Reset:         |                                                   |                                                                               |                                                                         |                                                         |                                              | •                                                            |                                                                 | et is exec                                          | <ul> <li>Software Reset</li> <li>Oscillation Stop Command</li> <li>cuted at the Write pulse. This is</li> </ul>                                                    |  |

| Oscillation Stop commar | nd: The<br>101<br>One<br>the<br>enu<br>Eve<br>reg | e Oscill<br>Ob is v<br>ce the<br>reafter,<br>umeration<br>en whe<br>isters, i | lation c<br>vritten i<br>IC goes<br>it is<br>on.<br>n the C<br>t is imp | ircuit o<br>in D7 to<br>s into t<br>necess<br>Dscillati | D4 (the stand<br>ary to<br>on has<br>to read | L6085<br>at is, w<br>dby sta<br>carry<br>stopped<br>d or wri | 1C stop<br>then At<br>te, to s<br>out a<br>d, altho<br>te the I | Oh is wr<br>start cor<br>gain d<br>bugh it<br>FIFO. | goes into the standby state when<br>ritten in this register).<br>nmunication with the USB bus<br>isconnecting, connecting, and<br>is possible to read on write the |  |

The oscillation can be started again by asserting the  $\overline{\text{RESET}}$  pin. The oscillation can be restarted even by a software reset.

### ML60851C

# bmRequest Type Setup Register

| Read address           |            | D      | 0h         |            |            |        |            |    |                                                          |

|------------------------|------------|--------|------------|------------|------------|--------|------------|----|----------------------------------------------------------|

| Write address          |            | _      | _          |            |            |        |            |    |                                                          |

|                        | <b>D</b> 7 | Do     | <b>D</b> 5 | <b>D</b> 4 | <b>D</b> 0 | Do     | <b>D</b> 4 | Do |                                                          |

|                        | D7         | D6     | D5         | D4         | D3         | D2     | D1         | D0 |                                                          |

| After a hardware reset | 0          | 0      | 0          | 0          | 0          | 0      | 0          | 0  |                                                          |

| After a bus reset      | 0          | 0      | 0          | 0          | 0          | 0      | 0          | 0  |                                                          |

| Definition             |            | Ту     | ре         |            | Rec        | eiving | side       |    |                                                          |

|                        |            |        |            |            |            |        |            |    |                                                          |

|                        |            |        |            |            |            |        |            |    |                                                          |

|                        |            |        |            |            |            |        |            |    | 0 = Device                                               |

|                        |            |        |            |            |            |        |            |    | 1 = Interface                                            |

|                        |            |        |            |            |            |        |            |    | – 2 = End point                                          |

|                        |            |        |            |            |            |        |            |    | 3 = Others                                               |

|                        |            |        |            |            |            |        |            |    | 4 to 31 = Reserved                                       |

|                        |            |        |            |            |            |        |            |    | 0 = Standard                                             |

|                        |            |        |            |            |            |        |            |    | _ 1 = Class                                              |

|                        |            |        |            |            |            |        |            |    | 2 = Vendor                                               |

|                        |            |        |            |            |            |        |            |    | 3 = Reserved                                             |

|                        |            | - Data | Transf     | er Direo   | ction      |        |            |    | ost computer to the device<br>evice to the host computer |

The format of the device request conforms to Section 9.3 of the USB standards. The eight bytes of setup data sent by the host computer during the setup stage of control transfer are stored automatically in eight registers including this register.

# **bRequest Setup Register**

| Read address           | D1h |    |    |       |         |    |    |    |

|------------------------|-----|----|----|-------|---------|----|----|----|

| Write address          |     | -  | _  |       |         |    |    |    |

|                        |     |    |    |       |         |    |    |    |

|                        | D7  | D6 | D5 | D4    | D3      | D2 | D1 | D0 |

| After a hardware reset | 0   | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

| After a bus reset      | 0   | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

| Definition             |     |    |    | Reque | st Code | ;  |    |    |

The request code indicating the contents of the device request is stored automatically in this register during the setup stage of control transfer.

## ML60851C

# wValue LSB Setup Register

| Read address           |    | D  | 2h |    |    |    |  |

|------------------------|----|----|----|----|----|----|--|

| Write address          |    | -  | _  |    |    |    |  |

|                        |    | 1  | 1  |    |    |    |  |

|                        | D7 | D6 | D5 | D4 | D3 | D2 |  |

| After a hardware reset | 0  | 0  | 0  | 0  | 0  | 0  |  |

| After a bus reset      | 0  | 0  | 0  | 0  | 0  | 0  |  |

| Definition |  | wValu | e L |

|------------|--|-------|-----|

A parameter of device request is stored in this register during the setup stage of control transfer.

SB

D1

0

0

D0

0

0

## wValue MSB Setup Register

| Read address  | D3h |

|---------------|-----|

| Write address | —   |

|                        | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|------------|----|----|----|----|----|----|----|

| After a hardware reset | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | wValue MSB |    |    |    |    |    |    |    |

A parameter of device request is stored in this register during the setup stage of control transfer.

# wIndex LSB Setup Register

| Read address  | D4h |

|---------------|-----|

| Write address |     |

|                        | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|------------|----|----|----|----|----|----|----|

| After a hardware reset | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | wIndex LSB |    |    |    |    |    |    |    |

A parameter of device request is stored in this register during the setup stage of control transfer.

## wIndex MSB Setup Register

| Read address  | D5h |

|---------------|-----|

| Write address |     |

|                        | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|------------|----|----|----|----|----|----|----|

| After a hardware reset | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | wIndex MSB |    |    |    |    |    |    |    |

A parameter of device request is stored in this register during the setup stage of control transfer.

# ML60851C

# wLength LSB Setup Register

| Read address           |    | D  | 6h |    |    |    |    |  |

|------------------------|----|----|----|----|----|----|----|--|

| Write address          |    | -  |    |    |    |    |    |  |

|                        |    |    |    |    |    |    |    |  |

|                        | D7 | D6 | D5 | D4 | D3 | D2 | D1 |  |

| After a hardware reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| After a bus reset      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

Definition wLength LSB

A parameter of device request is stored in this register during the setup stage of control transfer.

D0

0

# wLength MSB Setup Register

| Read address  | D7h |

|---------------|-----|

| Write address | _   |

|                        | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|-------------|----|----|----|----|----|----|----|

| After a hardware reset | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| After a bus reset      | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Definition             | wLength MSB |    |    |    |    |    |    |    |

A parameter of device request is stored in this register during the setup stage of control transfer.

# ML60851C

# Polarity Selection Register (POLSEL)

| Read address           |    | D, | Ah      |         |         |         |    |    |                                                                                                                                                                                                                                             |

|------------------------|----|----|---------|---------|---------|---------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write address          |    | 5/ | ۹h      |         |         |         |    |    |                                                                                                                                                                                                                                             |